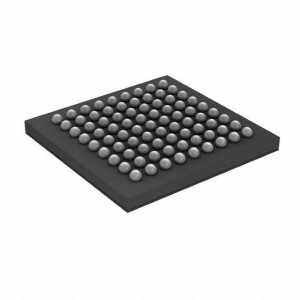

TMS320VC5509AZAY Digitala signalprocessorer och kontroller – DSP, DSC Fixed-Point Digital Signal Processor 179-NFBGA -40 till 85

♠ Produktbeskrivning

| Produktattribut | Attributvärde |

| Tillverkare: | Texas instrument |

| Produktkategori: | Digitala signalprocessorer och styrenheter - DSP, DSC |

| RoHS: | Detaljer |

| Produkt: | DSP:er |

| Serier: | TMS320VC5509A |

| Monteringsstil: | SMD/SMT |

| Paket/fodral: | NFBGA-179 |

| Kärna: | C55x |

| Antal kärnor: | 1 kärna |

| Maximal klockfrekvens: | 200 MHz |

| L1 Cache-instruktionsminne: | - |

| L1 cachedataminne: | - |

| Programminnesstorlek: | 64 kB |

| Data RAM-storlek: | 256 kB |

| Driftspänning: | 1,6 V |

| Lägsta driftstemperatur: | -40 C |

| Maximal drifttemperatur: | + 85 C |

| Förpackning: | Bricka |

| Varumärke: | Texas instrument |

| Instruktionstyp: | Fixpunkt |

| Gränssnittstyp: | I2C |

| Fuktkänslig: | Ja |

| Produkttyp: | DSP - Digitala signalprocessorer och styrenheter |

| Fabriksförpackningsmängd: | 160 |

| Underkategori: | Inbyggda processorer och kontroller |

| Matningsspänning - Max: | 1,65 V |

| Matningsspänning - Min: | 1,55 V |

| Watchdog Timers: | Watchdog Timer |

♠ TMS320VC5509A Digital signalprocessor med fast punkt

TMS320VC5509A digital signalprocessor (DSP) med fast punkt är baserad på TMS320C55x DSP-generationens CPU-processorkärna.C55x™ DSP-arkitekturen uppnår hög prestanda och låg effekt genom ökad parallellitet och totalt fokus på minskad effektförlust.CPU:n stöder en intern bussstruktur som är sammansatt av en programbuss, tre dataläsbussar, två dataskrivbussar och ytterligare bussar dedikerade till perifer och DMA-aktivitet.Dessa bussar ger möjlighet att utföra upp till tre dataläsningar och två dataskrivningar i en enda cykel.Parallellt kan DMA-styrenheten utföra upp till två dataöverföringar per cykel oberoende av CPU-aktiviteten.

C55x-processorn har två MAC-enheter (multiplicera-ackumulera), var och en kan 17-bitars x 17-bitars multiplikation i en enda cykel.En central 40-bitars aritmetisk/logisk enhet (ALU) stöds av ytterligare en 16-bitars ALU.Användning av ALU:erna är under instruktionsuppsättningskontroll, vilket ger möjlighet att optimera parallell aktivitet och energiförbrukning.Dessa resurser hanteras i adressenheten (AU) och dataenheten (DU) på C55x CPU.

C55x DSP-generationen stöder en instruktionsuppsättning med variabel bytebredd för förbättrad koddensitet.Instruktionsenheten (IU) utför 32-bitars programhämtningar från internt eller externt minne och köer instruktioner för programenheten (PU).Programenheten avkodar instruktionerna, dirigerar uppgifter till AU- och DU-resurser och hanterar den fullt skyddade pipelinen.Förutsägande förgreningsförmåga undviker pipelinespolningar vid exekvering av villkorliga instruktioner.

De allmänna in- och utgångsfunktionerna och 10-bitars A/D ger tillräckligt med stift för status, avbrott och bit-I/O för LCD-skärmar, tangentbord och mediagränssnitt.Det parallella gränssnittet fungerar i två lägen, antingen som en slav till en mikrokontroller som använder HPI-porten eller som ett parallellt mediagränssnitt med den asynkrona EMIF.Seriella media stöds av två MultiMedia Card/Secure Digital (MMC/SD) kringutrustning och tre McBSP:er.

5509A periferiuppsättningen inkluderar ett externt minnesgränssnitt (EMIF) som ger limlös åtkomst till asynkrona minnen som EPROM och SRAM, såväl som till höghastighetsminnen med hög densitet som synkront DRAM.Ytterligare kringutrustning inkluderar Universal Serial Bus (USB), realtidsklocka, watchdog-timer, I2C multi-master och slavgränssnitt.Tre full-duplex flerkanaliga buffrade seriella portar (McBSP) ger ett limfritt gränssnitt till en mängd industristandardiserade seriella enheter och flerkanalskommunikation med upp till 128 separat aktiverade kanaler.Det förbättrade värdportgränssnittet (HPI) är ett 16-bitars parallellt gränssnitt som används för att ge värdprocessoråtkomst till 32K byte internt minne på 5509A.HPI:n kan konfigureras i antingen multiplexerat eller icke-multiplexerat läge för att ge ett limfritt gränssnitt till en mängd olika värdprocessorer.DMA-styrenheten tillhandahåller datarörelse för sex oberoende kanalkontexter utan CPU-intervention, vilket ger DMA-genomströmning på upp till två 16-bitars ord per cykel.Två allmänna timers, upp till åtta dedikerade I/O-stift (GPIO) och digital faslåst loop (DPLL) klockgenerering ingår också.

5509A stöds av branschens prisbelönta eXpressDSP™, Code Composer Studio™ Integrated Development Environment (IDE), DSP/BIOS™, Texas Instruments algoritmstandard och branschens största tredjepartsnätverk.Code Composer Studio IDE har kodgenereringsverktyg inklusive en C-kompilator och Visual Linker, simulator, RTDX™, XDS510™-emuleringsenhetsdrivrutiner och utvärderingsmoduler.5509A stöds också av C55x DSP Library som innehåller mer än 50 grundläggande mjukvarukärnor (FIR-filter, IIR-filter, FFTs och olika matematiska funktioner) samt chip- och kortstödsbibliotek.

TMS320C55x DSP-kärnan skapades med en öppen arkitektur som tillåter tillägg av applikationsspecifik hårdvara för att öka prestanda på specifika algoritmer.Hårdvarutilläggen på 5509A har den perfekta balansen mellan prestanda för fasta funktioner och programmerbar flexibilitet, samtidigt som de uppnår låg strömförbrukning och kostnader som traditionellt har varit svåra att hitta på videoprocessormarknaden.Tilläggen gör att 5509A kan leverera exceptionell videocodec-prestanda med mer än halva bandbredden tillgänglig för att utföra ytterligare funktioner som färgrymdskonvertering, användargränssnitt, säkerhet, TCP/IP, röstigenkänning och text-till-tal-konvertering.Som ett resultat kan en enda 5509A DSP driva de flesta bärbara digitala videoapplikationer med bearbetningsutrymme över.För mer information, se TMS320C55x Hardware Extensions for Image/Video Applications Programmer's Reference (litteraturnummer SPRU098).För mer information om hur du använder DSP-bildbehandlingsbiblioteket, se TMS320C55x bild-/videobehandlingsbiblioteksprogrammerares referens (litteraturnummer SPRU037).

• Högpresterande, lågeffekts TMS320C55x™ digital signalprocessor med fast punkt

− 9,26-, 6,95-, 5-ns Instruktionscykeltid

− 108-, 144-, 200 MHz klockfrekvens

− En/två instruktion(er) utförs per cykel

− Dubbla multiplikatorer [upp till 400 miljoner multiplikationsackumuleras per sekund (MMACS)]

− Två aritmetiska/logiska enheter (ALU)

− Tre interna data/operandläsbussar och två interna data/operandskrivbussar

• 128K x 16-bitars On-Chip RAM, sammansatt av:

− 64K byte RAM (DARAM) med dubbla åtkomst 8 block med 4K × 16-bitars

− 192K byte av Single-Access RAM (SARAM) 24 block av 4K × 16-bitars

• 64K byte av One-Wait-State On-Chip ROM (32K × 16-bitar)

• 8M × 16-bitars maximalt adresserbart externt minnesutrymme (synkront DRAM)

• 16-bitars externt parallellbussminne som stöder antingen:

− Externt minnesgränssnitt (EMIF) med GPIO-funktioner och limlöst gränssnitt för att:

− Asynkront statiskt RAM (SRAM)

− Asynkron EPROM

− Synchronous DRAM (SDRAM)

− 16-bitars parallellt förbättrat värdportgränssnitt (EHPI) med GPIO-funktioner

• Programmerbar lågeffektkontroll av sex enhetsfunktionella domäner

• On-Chip skanningsbaserad emuleringslogik

• On-Chip kringutrustning

− Två 20-bitars timer

− Watchdog Timer

− Six-Channel Direct Memory Access (DMA) Controller

− Tre serieportar som stöder en kombination av:

− Upp till 3 flerkanaliga buffrade serieportar (McBSP)

− Upp till 2 MultiMedia/Secure Digital Card Interfaces

− Programmerbar faslåst slingklockgenerator

− Sju (LQFP) eller åtta (BGA) allmänna I/O (GPIO) stift och ett utgångsstift för allmänt ändamål (XF)

− USB-slavport med full hastighet (12 Mbps) som stöder bulk-, avbrotts- och isokrona överföringar

− Inter-Integrated Circuit (I2C) Multi-Master och Slave Interface

−Realtidsklocka (RTC) med kristallingång, separat klockdomän, separat strömförsörjning

− 4-kanals (BGA) eller 2-kanals (LQFP) 10-bitars successiv approximation A/D

• IEEE Std 1149.1† (JTAG) Boundary Scan Logic

• Paket:

− 144-terminaler Quad Flatpack med låg profil (LQFP) (PGE-suffix)

− 179-Terminal MicroStar BGA™ (Ball Grid Array) (GHH Suffix)

− 179-terminaler blyfri MicroStar BGA™ (Ball Grid Array) (ZHH Suffix)

• 1,2-V kärna (108 MHz), 2,7-V – 3,6-VI/Os

• 1,35-V kärna (144 MHz), 2,7-V – 3,6-VI/Os

• 1,6-V kärna (200 MHz), 2,7-V – 3,6-VI/Os

• Hybrid-, el- och drivsystem (EV/HEV)

– Batterihanteringssystem (BMS)

– Inbyggd laddare

– Traction inverter

– DC/DC-omvandlare

– Startmotor/generator